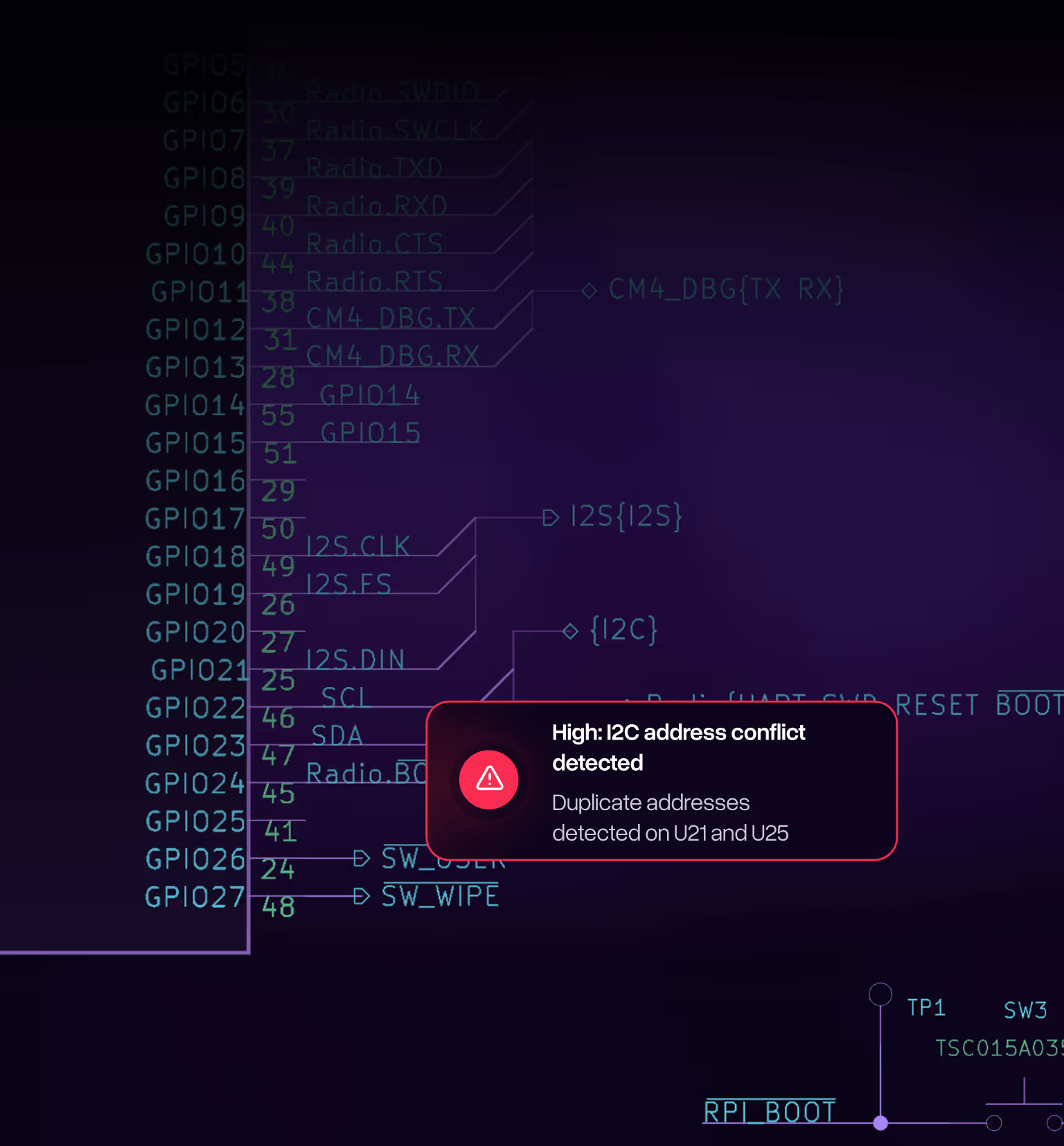

Catch PCB errors before they cost you weeks

Cadstrom checks the onerous details your ERC flow misses letting your team focus on the hard things

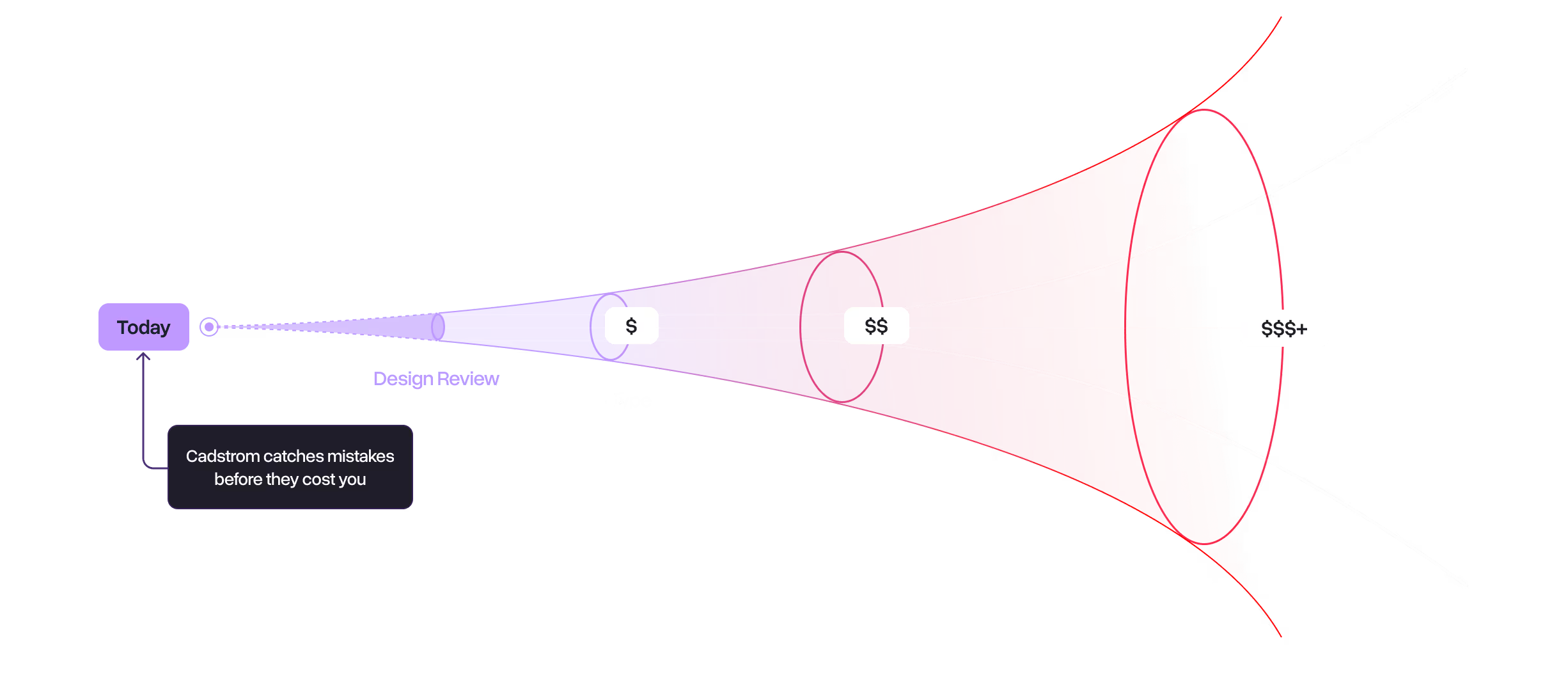

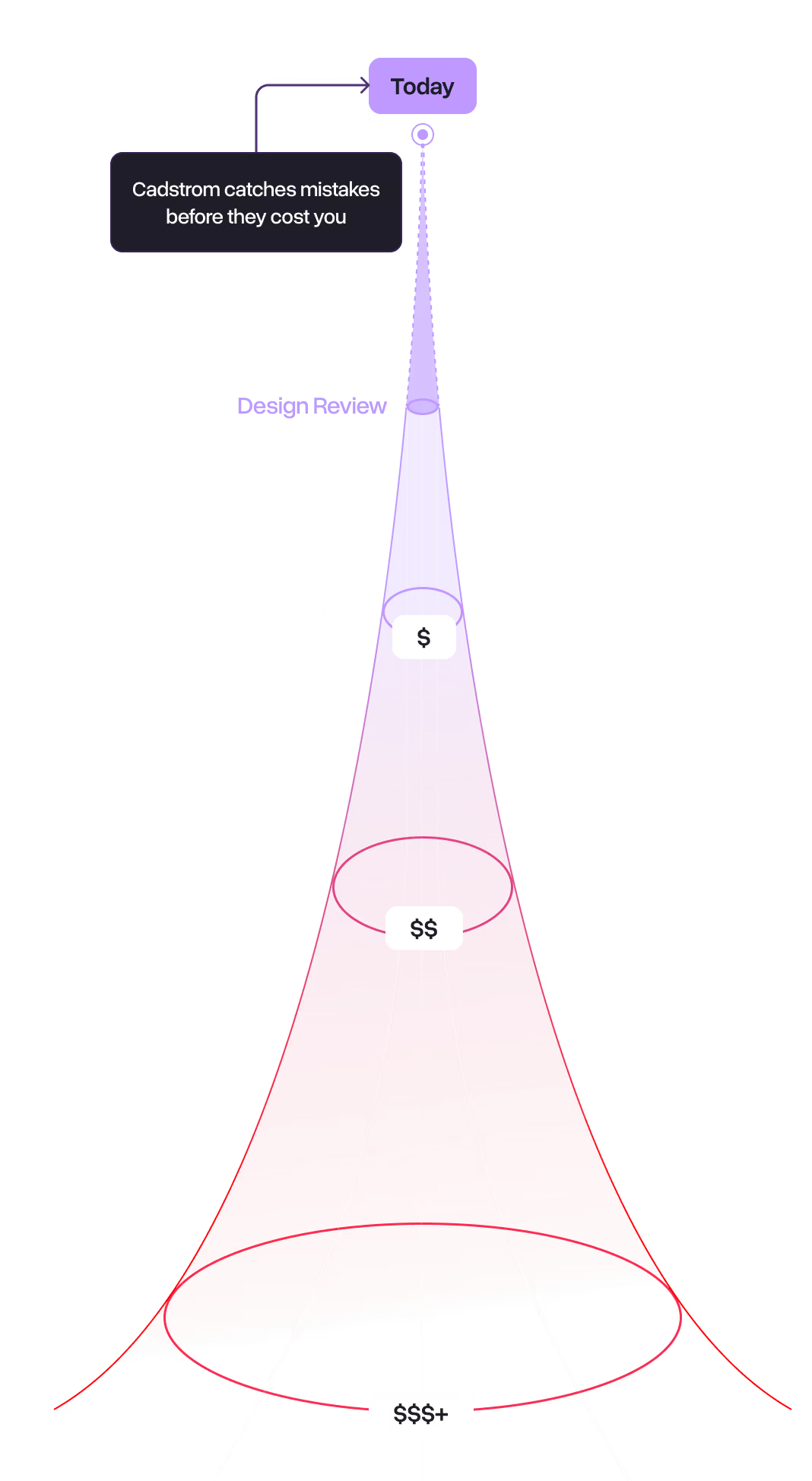

Mistakes don’t get cheaper

Cadstrom catches them before they cost you

10+ weeks

$30k+

Thousands

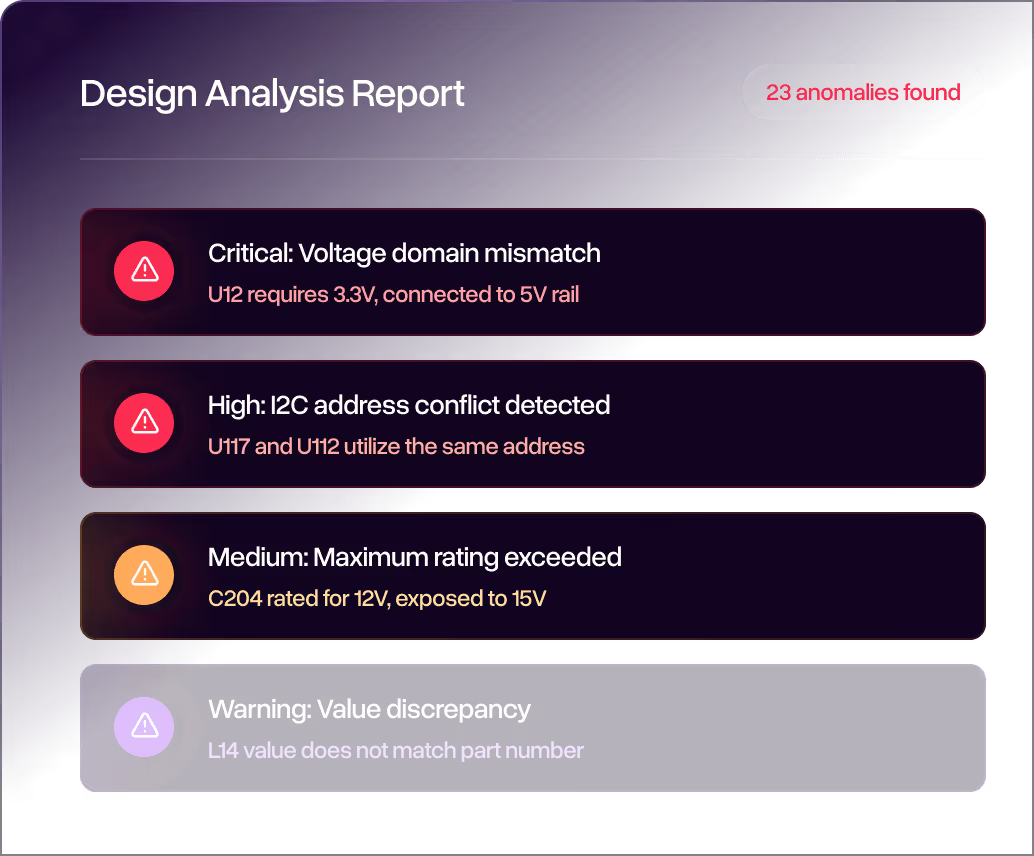

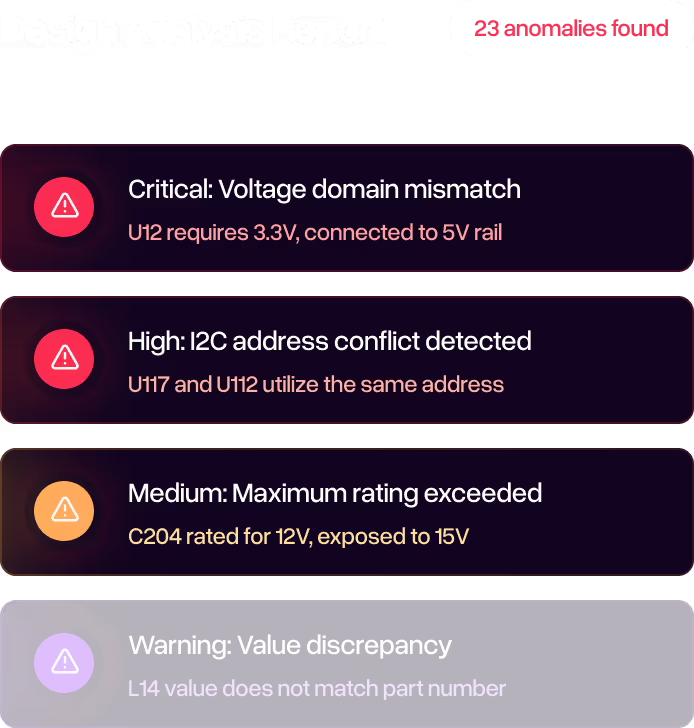

From review chaos to certainty

Automated validations catch what design reviews miss

Today's Best Practices

Engineers cope with disparate tools, fragmented processes, and manual checklists

With Cadstrom in your corner

Structured insights, deterministic results, and full confidence in every review

Why engineering teams rely on Cadstrom

For engineers who take pride in their work

Offload the tedious part of schematic review while keeping full control of your design.

Offload the tedious part of schematic review while keeping full control of your design. Catch the “I can’t believe I missed that” mistakes before they become expensive lab time.

Catch the “I can’t believe I missed that” mistakes before they become expensive lab time. Walk into design reviews without the stress - with a clear validation report, not hope.

Walk into design reviews without the stress - with a clear validation report, not hope.

For teams that accomplish more

Reduce project cost and schedules without hiring more engineers.

Reduce project cost and schedules without hiring more engineers. Turn ad-hoc review processes into repeatable and reliable validations.

Turn ad-hoc review processes into repeatable and reliable validations. Even one prevented respin can outweigh the cost of using Cadstrom many times over.

Even one prevented respin can outweigh the cost of using Cadstrom many times over.

Get time back to focus on the important things

Engineers who try Cadstrom never ship without it

Cadstrom exists so your team can move fast without gambling on “hope it’s fine” schematic reviews.

Margot has spent her career bringing groundbreaking technologies to market at Azure Quantum and Xbox. She sets the technical vision for Cadstrom from nearly a decade in hardware research.

Scott brings over 35 years of hands-on experience spanning electrical engineering, product development, and technology innovation.

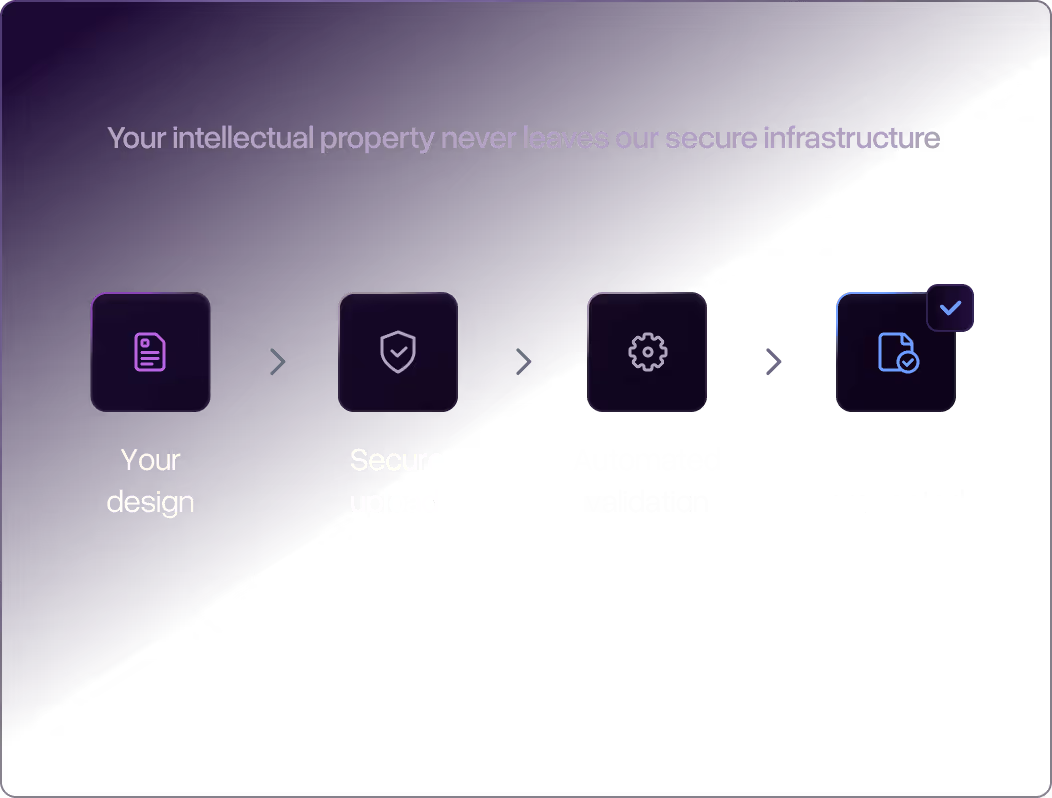

Built for the most sensitive designs

Cadstrom is built from the ground up to meet rigorous security and compliance requirements.

- End-to-end encryption

- AI never trains on IP

- SOC 2 controls in place

Your questions, answered clearly

Ready to eliminate respins?

See how Cadstrom can help you get hardware right the first time.